# 科学研究費助成事業 研究成果報告書

平成 30 年 5 月 21 日現在

機関番号: 34419

研究種目: 基盤研究(C)(一般)

研究期間: 2015~2017

課題番号: 15K05964

研究課題名(和文)デューティ比デジタル制御法によるリチウムイオンキャパシタ蓄電技術

研究課題名(英文)Energy storage technology with a Lithium ion capacitor using a digital control

method of duty ratio

### 研究代表者

中田 俊司 (NAKATA, Shunji)

近畿大学・工学部・准教授

研究者番号:40506218

交付決定額(研究期間全体):(直接経費) 2,400,000円

研究成果の概要(和文): リチウムイオンキャパシタを用いた電気エネルギー蓄電システム実現のために、緩やかにキャパシタを充電する断熱充電回路を設計した。この回路では、マイクロプロセッサを用いて、スイッチングトランジスタのデューティ比をデジタル的に制御した。充電効率は、電源の行った仕事とキャパシタの電気エネルギーの増加分の比として求められる。電源の行った仕事は、電源から流れ出た電荷量と電源電圧の積により求められる。実験から、充電時においても放電時においても、効率は95.5%となることが明らかとなった。充放電の1サイクルでは、91.2%の効率となる。この値は電気エネルギー蓄電システムを実現する上で良好な値である。

研究成果の概要(英文): An adiabatic charging circuit, which has the characteristic of the gradual charging of a capacitor, was designed for realizing an energy storage system with a Lithium ion capacitor. The duty ratio of the switching transistors is digitally controlled by a microprocessor. The charging efficiency is defined as the ratio between the work done by the power supply and the increase in electrostatic energy of the capacitor. The work done by the power supply is calculated from the product of the charge amount flowing from the power supply and the power supply voltage. Using this circuit, it is clarified experimentally that the efficiency is 95.5 % during charging and also discharging process. Then the total efficiency is 91.2 % during one cycle, which is a good value for realizing energy storage systems.

研究分野: 電気電子工学

キーワード: スーパーキャパシタ パワーエレクトロニクス デジタル制御 エネルギー散逸

### 1.研究開始当初の背景

本研究では、スーパーキャパシタを充放電 する際のエネルギー損失を零とするために、 断熱充電可逆回路に着眼した。断熱充電は、 Landauer や Feynman により考察され、原理的 には、キャパシタへの充放電過程において、 エネルギー損失を零とした可逆動作が可能 であることが基礎物理学の観点から指摘さ れた。しかしながら、具体的な回路を用いて 断熱充電を実現することは、30年以上進展が なかった。その後 1994 年に、具体的なタン クキャパシタを用いた回路構成により、断熱 充電を実現する方法が、Svensson と Koller により提案された。この方法は、N-1 個のタ ンクキャパシタを用いて等間隔のN個の電圧 を生成し、これらの電圧をキャパシタに順次 印加するという回路構成を用いる。この回路 により、キャパシタへの充放電のエネルギー 損失が 1/N 倍に低減することが示された。し かしながら、多くのタンクキャパシタを必要 とする点が問題であった。

このタンクキャパシタ増大の問題を解決する一つの方法は、インダクタLとキャパシタとの間で LC 共振回路を用いる回路構成であり、負荷容量に蓄積されたエネルギーをCMOS 回路を用いてエネルギーリサイクルを行い、これによりエネルギー損失の低減を行う回路が Restle らにより提案された。しかしながら、LC 共振回路では共振させる必要があるために、設計自由度が小さいという問題点があった。

これを解決するために、インダクタとスイッチングトランジスタを用いて、電源からの電流をデジタル的に制御して充電を行う回路方式が考案された[特許 5303178, 充電回路および充電方法]。この提案は、初期電圧 V<sub>i</sub>から最終電圧 V<sub>i</sub>までデューティ比を段階的に制御することにより段階的に充電し、かこその充電電圧を等間隔とすることにより、エネルギー散逸を最小とすることを特徴とている。すなわち、(V<sub>i</sub>-V<sub>i</sub>)/Nのステップ電圧幅で V<sub>i</sub>から V<sub>i</sub>まで充電する方法である。

これまでのところディスクリート IC を用いた回路により8 step の階段電圧を生成し、これら階段電圧により充放電を行う基礎的な研究を行ってきたが、この方法をさらに発展させるため、マイクロプロセッサにより、自由度の大きい、またステップ数の大きい充放電制御を行う事が期待された。

## 2.研究の目的

マイクロコンピュータを用いて、電源電圧の制御を1%単位で行い、きめ細かい電力の制御を行うことにより、エネルギーロスの無いリチウムイオンキャパシタの充放電技術を確立することを目的とする。さらにこのリチウムイオンキャパシタとエネルギーロスのない制御技術の組み合わせにより、夜間に電力を蓄電し、昼間に蓄電された電力を利用するという方法により、1日における電力使用

量の平準化実現の基礎となる回路技術への応用を検討することを目的とする。また、風力発電などの再生可能エネルギーの商用系統への接続を容易にするために、電力需給バランスに必要となる蓄電技術の確立を目指し、スマートグリッドの早期実現に貢献することを目的とする。

### 3.研究の方法

本研究では、この断熱充電回路の設計にお いて、デューティ比制御を PIC マイコンを用 いて行い、1%程度づつデジタル的にデューテ ィ比を変化させ 100 ステップ程度の階段電圧 の生成を行い、これらにより充放電を行う。 これにより、エネルギーロスが大きく低減す ることを明らかにする。PIC マイコンの制御 はC言語を用いることとし、研究期間内にお いてソフトウエア記述設計をおこない、PIC マイコンにおいて実際にスーパーキャパシ タへの充放電を行い、効率的なエネルギーの 蓄電が行えることを実証する。このために、 トランジスタは 10A 程度の電流を流すことが 可能なパワーMOSFETを用いることとする。本 研究により、マイコン制御による断熱充電回 路を進展させることができ、スマートグリッ ドへの応用を大きく前進させることが可能 となる。

本研究は蓄電デバイスとしてリチウムイオンキャパシタを用いることとした。このデバイスは今後の電気エネルギー蓄電に重要と考えられる。現在リチウムイオンバッテリが蓄電デバイスとして重要と位置付けられているが、充放電回数は 1000 回程度と短い点や、安全性の面で問題が残っている。一方、リチウムイオンキャパシタは充放電回数が10万回以上であり 100 倍寿命が長く、メインテナンスも 1 0 年程度は不要である。また、安全性も高く電気エネルギー蓄電デバイスとして今後優位となっていく可能性が高いと考えられる。

## 4. 研究成果

## (1) 回路構成

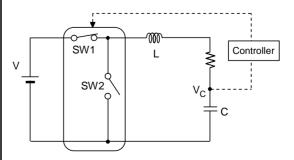

本研究は、キャパシタを充電する際に階段的な電圧を用いて行う事を特徴とする。これを実現するために、図1に示すように2個のスイッチングトランジスタとインダクタを用いる。キャパシタの電位をモニタし、その値によりスイッチングトランジスタを ON と

図1 充放電回路の基本構成

する割合であるデューティ比の制御が可能である。

## (2) 電気二重層キャパシタの充放電特性

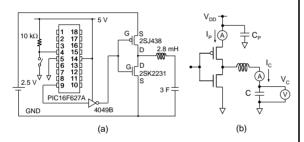

まず最初に電気二重層キャパシタを用いた実験結果について示す。図 2 に実験の回路構成を示す。デューティ比の制御は図 2 (a) にしめすように PIC マイコン (PIC16F627A) を用い、出力端子から PWM 波形を出力させることにより行った。図 1 の SW1, SW2 として PMOS の 2SJ438, nMOS の 2SK2231 のパワー MOSFET を用いた。電気二重層キャパシタの容量は 3F である。また充電電源電圧は、2.5Vとした。図 2 (b) は測定システムであり、キャパシタの電位  $V_{c}$ 、キャパシタに流れ込む電流  $I_{c}$ 、電源から流れ出る電流  $I_{c}$ をデジタルマルチメータにより測定した。 PWM 波形の周波数は、10.7kHz としている。

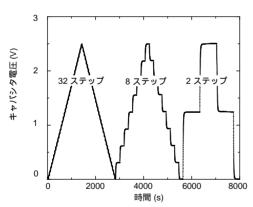

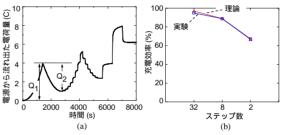

階段電圧による充電の有効性を示すために、32,8,2 ステップの階段電圧を生成し、これらにより充放電を行った。このときの Vo

図2 実験の回路構成: (a)マイクロプロセッサによる制御回路. (b)測定システム

図3 キャパシタ電圧の時間変化

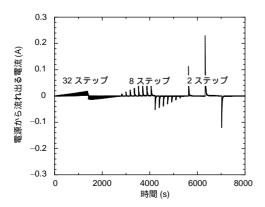

図4 電源電流の時間変化

の測定結果を図3に示す。32ステップ時には、 ほぼ直線で電圧が変化している。この時dは、 d=0,1/32,2/32,...,31/32,1,31/32,..., 1/32,0と変化させている。

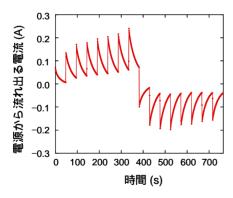

図4に I<sub>p</sub>の結果を示す。充電時には正の値であり放電時には負の値であるが、これは流れる方向が逆となることを示しおり、キャパシタからインダクタを通って電源に電流が戻ることを意味している。

次に充電効率  $_1$  を求めるために、電源から流れ出た電荷量  $Q_1$  を求めた。 $Q_1$  は  $I_p$  を積分することにより得られ、その結果を図 5 (a)に示す。32 ステップの充電時、 $Q_1$  の値は、3.93 C となる。電源の行った仕事  $W_1$  は電源電圧 V と  $Q_1$  を用いると  $W_1$ =  $Q_1$  V であるので、 $W_1$ =9.83 J が得られる。これに対しキャパシタの電気エネルギーE は、 $V_M$  をキャパシタの最大電位とすると  $E=CV_M^2/2$  と表せる。図 3 より  $V_M$  は 2.49 V であり、これから E=9.33 J が得られる。以上の結果から、  $_1$ =  $E/W_1$ =94.9%が得られる。

図5 測定結果の解析: (a)電源から流れ出る電荷量, (b)充電効率

理論的には、N ステップ充電の時、充電効率 1th は 1th=N/(N+1)と求められる。32 ステップでは理論値は 97.0%となり、実験値は理論値とほぼ一致する。同様に 8,2 ステップにおいて充電効率の理論値を計算し、実験結果とまとめた結果を図 5 (b)に示す。実験は理論とよく一致していることがわかる。

次に放電効率  $_2$ を議論する。  $_2$ はキャパシタが放電した電気エネルギーE に対して、電源がキャパシタから受け取るエネルギー $W_2$ の比率として定義できる。 $Q_2$ をキャパシタからインダクタを介して電源に戻る電荷量とすると、 $W_2$ は  $W_2$ = $Q_2$ V となる。図 5 (a)より $Q_2$ =2.94 C であり、 $W_2$ =7.34 J が得られる。よって、  $_2$ = $W_2$ /E=78.7%が得られる。

放電時に効率が低下している原因は、回路の抵抗成分のために、放電時に出力電圧が十分高い電圧にまで昇圧できないことなどが考えられる。これを解決するために、抵抗成分を極力低減する回路が有効と考えられる。

# (3) リチウムイオンキャパシタの充放電特性

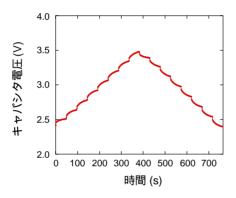

次に、リチウムイオンキャパシタを用いた 充放電特性を示す。リチウムイオンキャパシ タの容量は、36F のものを用いた。用いたリ チウムイオンキャパシタの許容最大電圧お よび最小電圧は、3.8および2.2Vであるので、 充電電圧をこの領域内とした。電源電圧の値を3.5Vとし、デューティ比を64/96,68/96,…,92/96,1,92/96,…,68/96,64/96と変化させ、8ステップによる充放電を行った。本実験においては回路の抵抗成分を極力低減させるために、基板にインダクタやトランジスタの実装を行った。

図6にキャパシタ電圧の測定結果を示す。デューティ比に対応して、キャパシタ電圧は、2.4から3.5Vの範囲にあることがわかる。図7に電源から流れ出る電流を示す。今回は充電時間を380sと短くしており、電流も図4と比較し、より連続的な変化を示している。この電流を積分した電源から流れ出た電荷量を図8に示す。Qは充電時電源から流れ出た電荷量であり、Qは放電時キャパシタから電源に戻った電荷量である。

充電時の効率 ₁は、この場合、キャパシタ

図6 リチウムイオンキャパシタ電圧の時間変化

図7 電源から流れ出る電流

図8 電源から流れ出た電荷量

の電気エネルギーの増分 E<sub>4</sub> を電源の行った 仕事 W<sub>4</sub> で割ったものになる。E<sub>4</sub> は E<sub>4</sub>=1/2·C (V,<sup>2</sup>-V,<sup>2</sup>)と表せる。ここで、V,および V, はキ ャパシタの最終電位および初期電位を表す。 これから充電時の効率を求めると、 』は =95.5%が得られる。また、放電時の効率  $_{2}=W_{2}/E_{2}$ となる。ここで、 $W_{2}$ はキャパシタ から電源に電流が流れ込むことによる電源 の受け取った仕事、E。は放電時におけるキャ パシタの電気エネルギーの減少分である。こ れから、放電時の効率っを求めると、 =95.5%が得られる。充放電の1サイクルに おける効率 は = 1 2であり、本実験では、 91.2%となり、良好な充放電特性が得られた。 このことは、電源からの電荷量の時間変化を 示す図 5 (a) と図 8 の比較でもわかる。仮に Q<sub>1</sub> = Q<sub>2</sub>となる場合には電源から流れ出た電荷 量が全て再び電源に戻る場合であり、このと =1 となる。Q, と Q, の値が近い場合には 効率が高いことになる。図8はQっとQoの値 が近くより効率が高いことが明確にわかる。 このことから、リチウムイオンキャパシタを 用い、回路構成素子を基板に実装した回路で は、非常に良好な充放電特性が実現できるこ とが明らかとなった。

今回の結果は、基礎的な研究であるが、今後電気自動車への応用や、スマートグリッドなどに応用がなされていくことが期待される。

本研究で得られた研究成果に対して、発表を行った学生が電気学会優秀論文発表賞、電気学会中国支部奨励賞、電子情報通信学会中国支部奨励賞を受賞しており、本研究の独創性および新規性が評価されている。

## 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## 〔雑誌論文〕(計4件)

Shunji Nakata, "An adiabatic charging reversible circuit with stepwise voltage control method using a microprocessor," Results in Physics, vol. 7, pp.2976-2978 (2017). 查読有.https://doi.org/10.1016/j.rinp.2017.08.024

中田俊司, "デューティ比デジタル制御法を用いたキャパシタ充電技術," 電気学会論文誌 C, vol.137, no. 10, pp. 1429-1430 (2017). 査読有.

https://doi.org/10.1541/ieejeiss.137 .1429

Shunji Nakata, Masaki Ono, and Masato Sakitani, "An Adiabatic Circuit with Consecutive Changes of the Duty Ratio of the Switching Transistor Using a Microprocessor," Journal of Circuits, Systems, and Computers, vol. 26, no. 1, 1750007/1-15 (2017). 查読有.

https://doi.org/10.1142/S02181266175 00074

<u>中田俊司</u>, "マイクロプロセッサによる 高効率スーパーキャパシタ蓄電回路技術 -Power MOSFET による電流制御," 近畿 大学工学部研究報告, vol.50, pp. 37-40 (2016). 査読無.

http://id.nii.ac.jp/1391/00018295/

#### [学会発表](計14件)

中田俊司、奥畠稜、合田満貴、「リチウム イオンキャパシタを用いた蓄電回路の電 気特性」、平成30年電気学会全国大会、 6-271、2018年3月14日~16日、九州大 学(福岡県福岡市)

猪原佑、中田俊司、「デジタル的デューティ比制御法を用いたスーパーキャパシタ充放電技術」、平成 29 年度電気・情報関連学会中国支部連合大会、R17-12-07、2017年10月21日、岡山理科大学(岡山県岡山市)

奥畠稜、合田満貴、<u>中田俊司</u>、「リチウム イオンキャパシタを蓄電デバイスとする 充放電回路の電気特性( )」、平成 29 年 度電気・情報関連学会中国支部連合大会、 R17-12-08、2017 年 10 月 21 日、岡山理 科大学(岡山県岡山市)

合田満貴、奥畠稜、<u>中田俊司</u>、「リチウム イオンキャパシタを蓄電デバイスとする 充放電回路の電気特性( )」、平成 29 年 度電気・情報関連学会中国支部連合大会、 R17-12-09、2017 年 10 月 21 日、岡山理 科大学(岡山県岡山市)

甲斐亮太、田畑大輝、槙大輔、<u>中田俊司</u>、「デューティ比デジタル制御法による高効率4直列キャパシタモジュール蓄電技術」平成29年電気学会全国大会、6-291、2017年3月15日~17日、富山大学(富山県富山市)

中田俊司、「スイッチングトランジスタのデューティ比制御法による高効率キャパシタモジュール蓄電技術」、平成28年電気学会電力・エネルギー部門大会、P29、2016年9月7日~9日、九州工業大学(福岡県北九州市)

中田俊司、「デューティ比デジタル制御法による高効率スーパーキャパシタ蓄電技術」、平成 28 年電気学会全国大会、6-283、2016 年 3 月 16 日~18 日、東北大学(宮城県仙台市)

中田俊司、小野雅貴、崎谷正人、「マイクロプロセッサを用いたスイッチングトランジスタのデューティ比制御法による高効率スーパーキャパシタ蓄電技術」平成27年電気学会電力・エネルギー部門大会、111、2015年8月25日~27日、名城大学(愛知県名古屋市)

### 〔産業財産権〕

出願状況(計1件)

名称:キャパシタの充放電回路

発明者:中田俊司 権利者:近畿大学 種類:特許

番号: 特願 2017-104029

出願年月日:2017年5月25日

国内外の別:国内

### 6.研究組織

### (1)研究代表者

中田 俊司 (NAKATA, Shunji) 近畿大学・工学部・准教授 研究者番号: 40506218

# (2)研究分担者

なし